# THOMSON SEMICONDUCTORS

### EF6845

#### ADVANCE INFORMATION

#### CRT CONTROLLER (CRTC)

The EF6845 CRT Controller performs the interface to raster scan CRT displays. It is intended for use in processor-based controllers for CRT terminals in stand-alone or cluster configurations.

The CRTC is optimized for hardware/software balance in order to achieve integration of all key functions and maintain flexibility. For instance, all keyboard functions, R/W, cursor movements, and editing are under processor control; whereas the CRTC provides video timing and Refresh Memory Addressing.

Applications include "glass-teletype," smart, programmable, intelligent CRT terminals; video games; information display.

Alphanumeric, semi-graphic, and full graphic capability.

- Fully programmable via processor data bus. Can generate timing for almost any alphanumeric screen density, e.g. 80 x 24, 72 x 64, 132 x 20. etc.

- Single +5 volt supply, TTL 6800 compatible I/O.

- Hardware scroll (paging or by line or by character)

- · Compatible with CPU's and MPU's which provide a means for synchronizing external devices.

- Cursor register and compare circuitry.

- Cursor format and blink are programmable.

- Light pen register.

- Line buffer-less operation. No external DMA required. Refresh Memory is multiplexed between CRTC and MPU.

- Programmable interlace or non-interlace scan.

- 14-bit wide refresh address.

### MOS

(N-CHANNEL, SILICON-GATE)

CRT CONTROLLER (CRTC)

#### THOMSON SEMICONDUCTORS

Sales headquarters 45, av. de l'Europe - 78140 VEL+ZY - FRANCE Tel. : (3) 946 97 19 / Telex : 204780 F

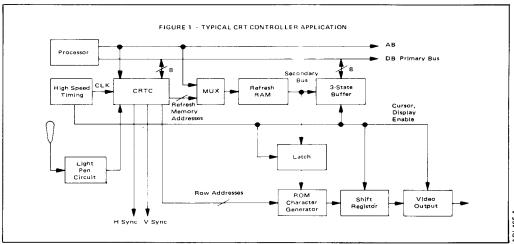

#### SYSTEM BLOCK DIAGRAM DESCRIPTION

As shown in Figure 1, the primary function of the CRTC is to generate refresh addresses (MAO-MA13), row selects (RAO-RA4), and video monitor timing (HSYNC, VSYNC) and Display Enable. Other functions include an internal cursor register which generates a Cursor output when its contents compare to the current Refresh Address. A light-pen strobe input signal allows capture of Refresh Address in an internal light pen register.

All timing in the CRTC is derived from the Clk input. In alphanumeric terminals, this signal is the character rate. Character rate is divided down from video rate by external High Speed Timing when the video frequency is greater than 3 MHz. Shift Register, Latch, and MUX Control signals are also provided by external High Speed Timing.

The processor communicates with the CRTC through a buffered 8-bit Data Bus by reading/writing into the 18-register file of the CRTC.

The Refresh Memory address is multiplexed between the Processor and CRTC. Data appears on a Secondary Bus which is buffered from the processor Primary Bus. A number of approaches are possible for solving contentions for the Refresh Memory.

- 1. Processor always gets priority.

- Processor gets priority access anytime, but can be synchronized by an interrupt to perform accesses only during horizontal and vertical retrace times.

- 3. Synchronize processor by memory wait cycles.

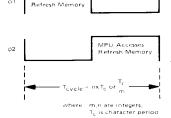

- 4. Synchronize processor to character rate (See Figure 2). The 6800 MPU family lends itself to this configuration because it has constant cycle lengths. This method provides zero burden on the processor because there is never a contention for memory. All accesses are "transparent."

The secondary data bus concept in no way precludes using the Refresh RAM for other purposes. It looks like any other RAM to the Processor. For example, using Approach 4, a 64K byte RAM Refresh Memory could perform refresh and program storage functions transparently.

#### MAXIMUM RATINGS

| Rating                      | Symbol            | Value        | Unit |

|-----------------------------|-------------------|--------------|------|

| Supply Voltage              | vcc*              | -0.3 to +7.0 | Vdc  |

| Input Voltage               | V <sub>in</sub> * | -0.3 to +7.0 | Vdc  |

| Operating Temperature Range | TA                | 0 to +70     | пC   |

| Storage Temperature Range   | Tstg              | -55 to +150  | °C   |

<sup>\*</sup>With respect to VSS (Gnd).

#### RECOMMENDED OPERATING CONDITIONS

| Characteristics    | Symbol | Min  | Тур | Max  | Unit |

|--------------------|--------|------|-----|------|------|

| Supply Voltage     | Vcc    | 4.75 | 5.0 | 5.25 | Vdc  |

| Input Low Voltage  | VIL    | -0.3 |     | 8.0  | Vd¢  |

| Input High Voltage | VIH    | 2.0  |     | Vcc  | Vdc  |

FIGURE 2 - TRANSPARENT REFRESH MEMORY CONFIGURATION TIMING USING 6800 MPU FAMILY

CBTC Accesses

**ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 5.0 \text{ V } \pm 5\%$ ,  $V_{SS} = 0$ ,  $T_A = 0$  to  $70^{\circ}\text{C}$  unless otherwise noted)

| Characteristic                                                                        |                        | Symbol                            | Min        | Тур    | Max        | Unit |

|---------------------------------------------------------------------------------------|------------------------|-----------------------------------|------------|--------|------------|------|

| Input High Voltage                                                                    |                        | VIH                               | 2.0        |        | Vcc        | Vdc  |

| Input Low Voltage                                                                     |                        | VIL                               | -0.3       | 1 - 1  | 8.0        | Vdc  |

| Input Leakage Current                                                                 |                        | Lin                               | _          | 1.0    | 2.5        | μAdc |

| Three-State (V <sub>CC</sub> = 5.25 V)<br>(V <sub>in</sub> = 0.4 to 2.4 V)            |                        | <sup>I</sup> TS1                  | -10        | 2.0    | 10         | μAdc |

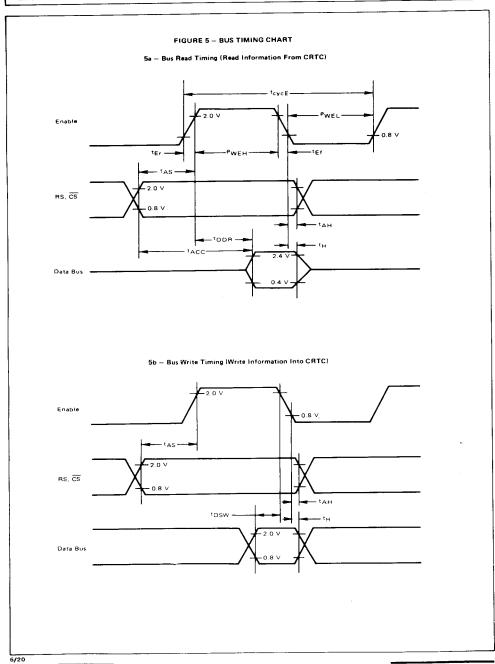

| Output High Voltage<br>{I <sub>(Oad</sub> = -205 µA)<br>(I <sub>(Oad</sub> = -100 µA) | D0-D7<br>Other Outputs | VOH                               | 2.4<br>2.4 | _<br>_ | _          | Vdc  |

| Output Low Voltage<br>(I <sub>load</sub> = 1.6 mA)                                    |                        | VOL                               | _          | -      | 0.4        | Vdc  |

| Power Dissipation                                                                     |                        | PD                                |            | 600    |            | mW   |

| Input Capacitance                                                                     | D0-D7<br>All others    | C'IU                              | -          | -      | 12.5<br>10 | pF   |

| Output Capacitance                                                                    | All Outputs            | Cout                              | -          | -      | 10         | pF   |

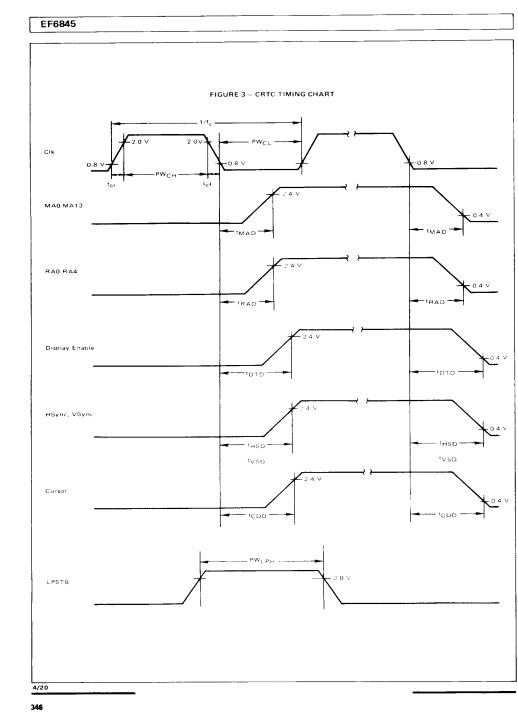

| Minimum Clock Pulse Width, Low                                                        |                        | PWCL                              | 160        | _      |            | ns   |

| Minimum Clock Pulse Width, High                                                       |                        | PWCH                              | 200        | -      |            | ns   |

| Clock Frequency                                                                       |                        | f <sub>c</sub>                    |            | -      | 2.5        | MHz  |

| Rise and Fall Time for Clock Input                                                    |                        | t <sub>cr</sub> , t <sub>cf</sub> |            | 1 - 1  | 20         | ns   |

| Memory Address Delay Time                                                             | <u> </u>               | <sup>‡</sup> MAD                  |            |        | 160        | ns   |

| Raster Address Delay Time                                                             | <u> </u>               | †RAD                              |            | _      | 160        | ns   |

| Display Timing Delay Time                                                             |                        | <sup>t</sup> DTD                  | _          | -      | 300        | ns   |

| Horizontal Sync Delay Time                                                            |                        | tHSD                              |            | - "    | 300        | ns   |

| Vertical Sync Delay Time                                                              |                        | tvsD                              |            |        | 300        | ns   |

| Cursor Display Timing Delay Time                                                      |                        | ¹CDD                              | _          | -      | 300        | ns   |

| Light Pen Strobe Minimum Pulse Width                                                  |                        | PWLPH                             | 100        | -      |            | ns   |

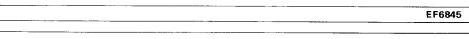

| Light Pen Strobe Disable Time                                                         |                        | †LPD1                             |            | _      | 120        | ns   |

|                                                                                       |                        | tLPD2                             | -          |        | 0          | ns   |

Note: The light pen strobe must fall to low level before VSYNC pulse rises

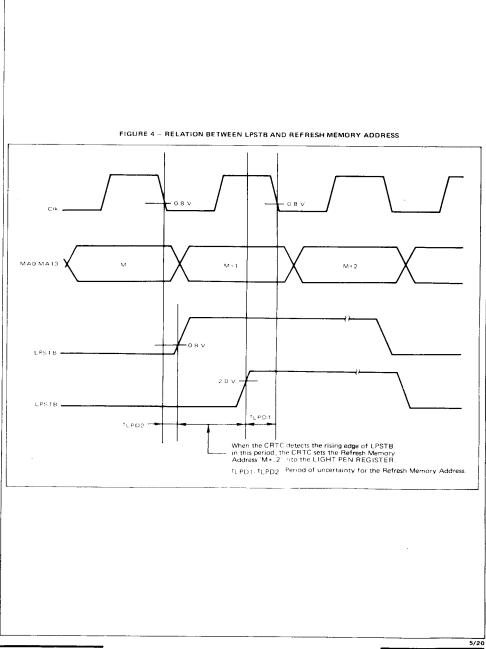

#### **BUS TIMING CHARACTERISTICS**

| Unit | Max | Min      | Symbol           | Characteristic                                            |

|------|-----|----------|------------------|-----------------------------------------------------------|

|      |     |          |                  | READ/WRITE                                                |

| μs   |     | 1.0      | †cycE            | Enable Cycle Time                                         |

| μς   | 25  | 0.45     | PWEH             | Enable Pulse Width, High                                  |

| μs   |     | 0.43     | PWEL             | Enable Pulse Width, Low                                   |

| ns   | -   | 160      | tAS              | Setup Time, CS and RS valid to enable positive transition |

| ns   | 320 | -        | tDDR             | Data Delay Time                                           |

| ns   |     | 10<br>10 | tн               | Data Hold Time (Read)<br>(write)                          |

| ns   |     | 10       | t <sub>AH</sub>  | Address Hold Time                                         |

| ns   | 25  |          | ter, tet         | Rise and Fall Time for Enable Input                       |

| ns   | -   | 195      | t <sub>DSW</sub> | Data Setup Time                                           |

| ns   | 480 |          | tACC             | Data Access Time                                          |

|      | -   | 195      | t <sub>DSW</sub> | Data Setup Time                                           |

This Material Copyrighted By Its Respective Manufacturer

348

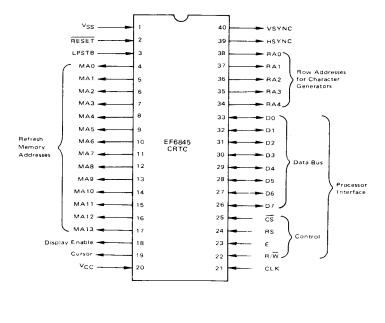

#### FIGURE 7 - PIN ASSIGNMENT

#### PIN DESCRIPTION

#### PROCESSOR INTERFACE

The CRTC interfaces to a processor bus on the bidirectional data bus (D0-D7) using  $\overline{CS}$ , RS, E, and R/ $\overline{W}$  for control signals.

Data Bus (D0-D7) — The bidirectional data lines (D0-D7) allow data transfers between the CRTC internal Register File and the processor. Data bus output drivers are 3-state buffers which remain in the high impedance state except when the processor performs a CRTC read operation. A high level on a data pin is a logical "1."

Enable (E) — The Enable signal is a high impedance TTL/MOS compatible input which enables the data bus input/output buffers and clocks data to and from the CRTC. This signal is usually derived from the processor clock, and the high to low transition is the active edge.

Chip Select (CS) — The CS line is a high impedance TTL/MOS compatible input which selects the CRTC when low to read or write the internal Register File. This signal should only be active when there is a valid stable address being decoded from the processor.

Register Select (RS) — The RS line is a high impedance TTL/MOS compatible input which selects either the Address Register (RS = "0") or one of the Data Registers (RS = "1") of the internal Register File.

Read/Write (R/ $\overline{W}$ ) — The R/ $\overline{W}$  line is a high impedance TTL/MOS compatible input which determines whether the internal Register File gets written or read. A write is active low ("0").

#### CRT CONTROL

The CRTC provides horizontal sync (HS), vertical sync (VS), and Display Enable signals.

Vertical Sync (V SYNC) — This TTL compatible output is an active high signal which drives the monitor directly or is fed to Video Processing Logic for composite generation. This signal determines the vertical position of the displayed text.

Horizontal Sync (H SYNC) — This TTL compatible output is an active high signal which drives the monitor directly or is fed to Video Processing Logic for composite generation. This signal determines the horizontal position of the displayed text.

Display Enable — This TTL compatible output is an active high signal which indicates the CRTC is providing addressing in the active Display Area.

## REFRESH MEMORY/CHARACTER GENERATOR ADDRESSING

The CRTC provides Memory Addresses (MAO-MA13) to scan the Refresh RAM. Also provided are Raster Addresses (RAO-RA4) for the character ROM.

Refresh Memory Addresses (MA0-MA13) — These 14 outputs are used to refresh the CRT screen with pages of data located within a 16K block of refresh memory. These outputs drive a TTL load and 30pF. A high level on MA0-MA13 is a logical "1."

Raster Addresses (RA0-RA4) — These 5 outputs from the internal Raster Counter address the Character ROM for the row of a character. These outputs drive a TTL load and 30pF. A high level (on RA0-RA4) is a logical "1."

#### OTHER PINS

Cursor — This TTL compatible output indicates Cursor Display to external Video Processing Logic. Active high signal.

Clock (CLK) — The CLK TTL/MOS compatible input is used to synchronize all CRT control signals. An external dot counter is used to derive this signal which is usually the character rate in an alphanumeric CRT. The active transition is high to low.

Light Pen Strobe (LPSTR) — This high impedance TTL/MOS compatible input latches the current Refresh Addresses in the Register File. Latching is on the low to high edge and is synchronized internally to character clock.

V<sub>CC</sub>, Gnd

RES - The RES input is used to Reset the CRTC. An input low level on RES forces CRTC into following status:

- (A) All the counters in CRTC are cleared and the device stops the display operation.

- (B) All the outputs go down to low level.

- (C) Control registers in CRTC are not affected and remain unchanged.

This signal is different from other 6800 family in the following functions:

- (A) RES signal has capability of reset function only when LPSTB is at low level.

- (B) After RES has gone down to low level, output signals of MAO-MA13 and RAO-RA4, synchronizing with CLK low level, goes down to low level. (At least 1 cycle CLK signal is necessary for reset.)

- (C) The CRTC starts the Display operation immediately after the release of RES signal.

TABLE 1 - CRTC Operating Mode

| RES | LPSTB | OPERATING MODE |

|-----|-------|----------------|

| 0   | 0     | Reset          |

| 0   | 1     | Test Mode      |

| 1   | 0     | Normal Mode    |

| 1   | 1     | Normal Mode    |

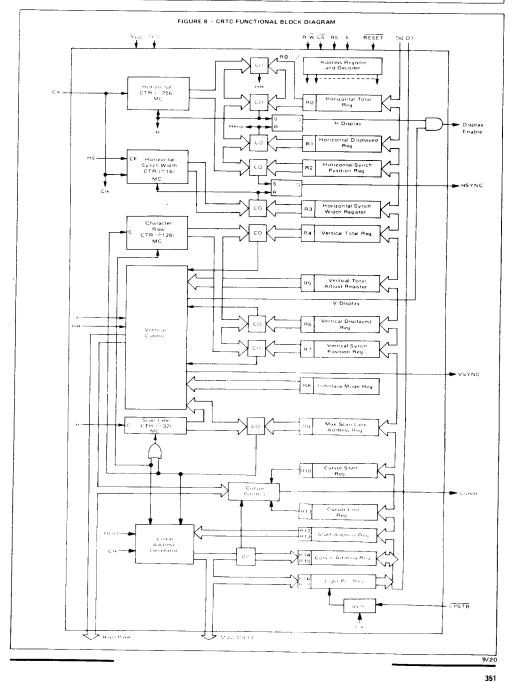

## CRTC DESCRIPTION (Figure 8: CRTC Block Diagram)

The CRTC consists of programmable horizontal and vertical timing generators, programmable linear address register, programmable cursor logic, light pen capture register, and control circuitry for interface to a processor bus.

All CRTC timing is derived from CLK, usually the output of an external dot rate counter. Coincidence (CO) circuits continuously compare counter contents to the contents of the programmable register file, RO-R17. For horizontal timing generation, comparisons result in: 1) Horizontal sync pulse (HS) of a frequency, position, and width determined by the registers, 2) Horizontal Display Signal of a frequency, position, and duration determined by the registers.

The Horizontal counter produces H clock which drives the Scan Line Counter and Vertical Control. The contents of the Raster Counter are continuously compared to the Max Scan Line Address Register. A coincidence resets the Raster Counter and clocks the Vertical Counter.

Comparisons of Vertical Counter contents and Vertical Registers result in: 1) Vertical sync pulse (VS) of a frequency and position determined by the registers- the width is fixed at 16 raster lines in the vertical control section and is not programmable, 2) Vertical Display of a frequency and position determined by the registers.

The Vertical Control Logic has other functions.

- Generate row selects, RAO-RA4, from the Raster Count for the corresponding interlace or noninterlace modes.

- Extend the number of scan lines in the vertical total by the amount programmed in the Vertical Total Adjust Register.

The Linear Address Generator is driven by CLK and locates the relative positions of characters in memory with their positions on the screen. Fourteen lines, MAO-MA13, are available for addressing up to four pages of 4K characters, 8 pages of 2K characters, etc. Using the Start Address Register, hardware scrolling through 16K characters is possible. The Linear Address Generator repeats the same sequence of addresses for each scan line of a character row.

The cursor logic determines the cursor location, size, and blinking rate on the screen. All are programmable.

The light pen strobe going high causes the current contents of the Address Counter to be latched in the Light Pen Register. The contents of the Light Pen Register are subsequently read by the Processor.

Internal CRTC registers are programmed by the processor through the data bus, D0-D7, and the control signals— $R\overline{W}$ ,  $\overline{CS}$ , RS and E.

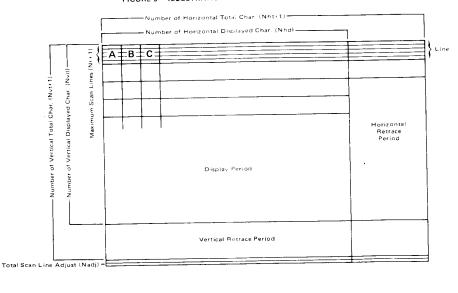

FIGURE 9 - ILLUSTRATION OF THE CRT SCREEN FORMAT

#### REGISTER FILE DESCRIPTION (See Table 2)

Nineteen registers in the CRTC can be accessed by means of the data bus. Register addressing and lengths are shown in Table 2.

#### ADDRESS REGISTER

The Address Register is a 5 bit write-only register used as an 'indirect'' or "pointer" register. Its contents are the address of one of the other 18 registers in the file. When RS and  $\overline{\text{CS}}$  are low, the Address Register itself is addressed. When RS is high, the Register File is accessed.

### HORIZONTAL TIMING REGISTERS RO, R1, R2, and R3

Figure 9 shows the visible display area of a typical CRT monitor giving the point of reference for horizontal registers as the left most displayed character position. Horizontal registers are programmed in "character time" units with respect to the reference.

Horizontal Total Register (R0) — This 8 bit write-only register determines the horizontal frequency of HS. It is the total of displayed plus non-displayed character time units minus one.

**Horizontal Displayed Register (R1)** – This 8 bit write-only register determines the number of displayed characters per horizontal line.

Horizontal Sync Position Register (R2) — This 8 bit write-only register determines the horizontal sync position on the horizontal line.

Horizontal Sync Width Register (R3) - This 4 bit

write-only register determines the width of the HS pulse. It may not be apparent why this width needs to be programmed. However, consider that all timing widths must be programmed as multiples of the character clock period which varies. If HS width were fixed as an integral number of character times, it would vary with character rate and be out of tolerance for certain monitors. The rate programmable feature allows compensating HS width.

## VERTICAL TIMING REGISTERS R4, R5, R6, R7, R8, and R9

The point of reference for vertical registers is the top character position displayed. Vertical registers are programmed in character row times or scan line times.

Vertical Total Register (R4) and Vertical Total Adjust Register (R5) — The vertical frequency of VS is determined by both R4 and R5. The calculated number of character line times is usually an integer plus a fraction to get exactly a 50 or 60 Hz vertical refresh rate. The integer number of character line times minus one is programmed in the 7 bit write-only Vertical Total Register; the fraction is programmed in the 5 bit write-only Vertical Scan Adjust Register as a number of scan line times.

Vertical Displayed Register (R6) — This 7 bit write-only register determines the number of displayed character rows on the CRT screen, and is programmed in character row times.

Vertical Sync Position (R7) — This 7 bit write-only register determines the vertical sync position with respect

TABLE 2 -- CRTC INTERNAL REGISTER ASSIGNMENT

| ſ  |    |    |   | Add | ress P | egist | or | Register |                       | Program   |      | Ī     | T |               | N             | umbe | r of E | lits |      |    |

|----|----|----|---|-----|--------|-------|----|----------|-----------------------|-----------|------|-------|---|---------------|---------------|------|--------|------|------|----|

|    | ζS | RS | 4 | 3   | 2      | 1     | 0  | ##       | Register File         | Unit      | Read | Write | 7 | 6             | 5             | 4    | 3      | 2    | 1    | 0  |

| [  | 1  | х  | × | ×   | ×      | ×     | ×  | ×        |                       |           | -    | -     |   |               |               |      | abla   |      |      |    |

|    | 0  | 0  | × | ×   | ×      | ×     | ×  | ×        | Address Register      |           | No   | Yes   |   |               | $\overline{}$ |      |        |      |      |    |

| Ţ  | 0  | 1  | 0 | 0   | 0      | 0     | 0  | R0       | Horizontal Total      | Char      | No   | Yes   |   |               |               |      |        |      |      |    |

| -  | 0  | 1  | 0 | 0   | 0      | 0     | 1  | R1       | Horizontal Displayed  | Char      | No   | Yes   |   |               | Π             |      |        |      |      | Г  |

| 1  | 0  | 1  | 0 | 0   | 0      | 1     | 0  | R2       | H Sync Position       | Char      | No   | Yes   |   |               |               |      |        |      |      | Г  |

| ĺ  | 0  | 1  | 0 | 0   | 0      | 1     | 1  | R3       | H. Sync Width         | Char      | No   | Yes   |   |               |               |      |        |      |      |    |

| [  | 0  | 1  | 0 | 0   | 1      | 0     | 0  | R4       | Vertical Total        | Char Row  | No   | Yes   |   |               |               |      |        |      |      |    |

| [  | 0  | 1  | 0 | 0   | 1      | 0     | 1  | R5       | V Total Adjust        | Scan Line | No   | Yes   |   |               |               |      |        |      |      |    |

| [  | 0  | 1  | 0 | 0   | 1      | 1     | 0  | R6       | Vertical Displayed    | Char Row  | No   | Yes   |   |               |               |      |        |      |      |    |

| ,[ | 0  | 1  | 0 | 0   | 1      | 1     | 1  | R7       | V Sync Position       | Char Row  | No   | Yes   |   |               |               |      |        |      |      | П  |

| ľ  | 0  | 1  | 0 | 1   | 0      | 0     | 0  | R8       | Interlace Mode        |           | No   | Yes   |   |               |               |      |        |      |      |    |

|    | 0  | 1  | 0 | 1   | 0      | 0     | 1  | R9       | Max Scan Line Address | Scan Line | No   | Yes   |   |               | $\overline{}$ |      |        |      |      |    |

| I  | 0  | 1  | 0 | 1   | О      | 1     | 0  | R10      | Cursor Start          | Scan Line | No   | Yes   |   | В             | Р             |      |        | (١   | lote | 1) |

|    | 0  | 1  | 0 | 1   | 0      | 1     | 1  | R11      | Cursor End            | Scan Line | No   | Yes   |   | V             |               |      |        |      |      |    |

| [  | 0  | 1  | 0 | 1   | 1      | 0     | 0  | R12      | Start Address (H)     |           | No   | Yes   |   |               |               |      |        |      |      |    |

| I  | 0  | 1  | 0 | 1   | 1      | 0     | 1  | . R13    | Start Address (L)     |           | No   | Yes   | I |               |               |      |        |      |      |    |

| I  | 0  | 1  | 0 | 1   | 1      | 1     | 0  | R14      | Cursor (H)            |           | Yes  | Yes   |   |               |               |      |        |      |      |    |

| [  | 0  | 1  | 0 | 1   | 1      | 1     | 1  | R15      | Cursor (L)            | LI        | Yes  | Yes   |   |               |               |      |        |      |      | Ī  |

| [  | 0  | 1  | 1 | 0   | 0      | 0     | 0  | R16      | Light Pen (H)         |           | Yes  | No    |   | $\overline{}$ |               |      |        |      |      |    |

| ſ  | 0  | 1  | 1 | 0   | 0      | 0     | 1  | B17      | Light Pen (L)         |           | Yes  | No    |   |               |               |      |        |      |      | П  |

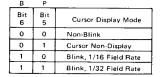

Note (1): Bit 5 of the Cursor Start Raster Register is used for blink period control, and

Bit 6 is used to select blink or non blink

to the reference. It is programmed in character row times.

Interlace Mode Register (R8) — This 2 bit write-only register controls the raster scan mode (see Figure 11). When bit 0 and bit 1 are reset, or bit 0 is reset and bit 1 set, the non-interlace raster scan mode is selected. Two interlace modes are available. Both are interlaced 2 fields per frame. When bit 0 is set and bit 1 is reset, the interlace sync raster scan mode is selected. Also when bit 0 and bit 1 are set, the interlace sync and video raster scan mode is selected.

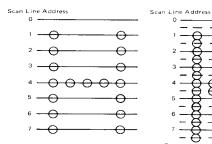

Maximum Scan Line Address Register (R9) — This 5 bit write-only register determines the number of scan lines per character row including spacing. The programmed value is a max address and is one less than the number of scan lines.

#### OTHER REGISTERS

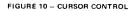

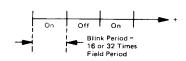

Cursor Start Register (R10) — This 7 bit write-only register controls the cursor format (see Figure 10). Bit 5 is the blink timing control. When bit 5 is low, the blink frequency is 1/16 of the vertical field rate, and when bit 5 is high, the blink frequency is 1/32 of the vertical field rate. Bit 6 is used to enable a blink. The cursor start scan line is set by the lower 5 bits.

Cursor End Register (R11) — This 5 bit write-only register sets the cursor end scan line.

Start Address Register (H & L) (R12, R13) — Start Address Register is a 14 bit write-only register which determines the first address put out as a refresh address after vertical blanking. It consists of an 8 bit lower register, and a 6 bit higher register.

Light Pen Register (H & L) (R16, R17) — This 14 bit read-only register is used to store the contents of the Address Register (H & L) when the LPSTB input pulses high. This register consists of an 8 bit lower and 6 bit higher register.

Cursor Register (H & L) (R14, R15) — This 14 bit read/write register stores the cursor location. This register consists of an 8 bit lower and 6 bit higher register.

#### CURSOR

The Cursor Start and End Registers allow a cursor of up to 32 scan lines in height to be placed on any scan lines of the character block as shown in Figure 10. Using Bits 5 & 6 of the Cursor Start Register, the cursor is programmed with blink periods of 16 or 32 times the field period. Optional non-blink and non-display modes can also be selected. When an external 2X blink on characters is required, it may be necessary to perform cursor blink externally as well so that both blink rates are synchronized. Note that an invert/non-invert cursor is easily implemented by programming the CRTC for blinking cursor and externally inverting the video signal with an exclusive-OR.

The cursor is positioned by changing the contents of registers R14 and R15. The cursor can be placed at any of 16K character positions, thus facilitating hardware paging and scrolling through memory without loss of the cursor's original position.

## INTERLACE/NON-INTERLACE DISPLAY MODES

An illustration of the 3 raster scan modes of operation is shown in Figure 11. Normal sync mode is non-interlace. In this mode, each scan line is refreshed at the vertical field rate (e.g., 50 or 60 Hz). Frame time is divided into even and odd alternating fields. The horizontal and vertical timing relationship results in the displacement of scan lines in the odd field with respect to the even field. When the same information is painted in both fields, the mode is called "Interlace Sync;" this is a useful mode for enhancing readability by filling in a character. When the even lines of a character are displayed in the even field and the odd lines in the odd field, the mode is called "Interlace Sync and Video." This last mode effectively doubles the character density on a monitor of a given bandwidth. The disadvantage of both interlace modes is an apparent flicker effect, which can be reduced by careful monitor design.

There are restrictions on the programming of CRTC registers for interlace operation:

- Horizontal total character count, N<sub>ht</sub> must be odd (i.e., an even number of character times)

- For Interlace Sync and Video mode only, the max scan line address, N<sub>sl</sub>, must be odd (i.e., an even number of scan lines)

- For Interlace Sync and Video mode only, the Vertical Displayed Total characters must be even. The programmed number, N<sub>vd</sub>, must be one-half the actual number required.

- For Interlace Sync & Video mode only, the Cursor START and Cursor End Registers must both be even or both odd.

#### LIGHT PEN

The contents of the CRTC Address Counter are strobed into R16/R17 Light Pen Registers on the next high to low CLK transition afterLPSTB goes high. In most systems, the light pen signal would also cause a processor interrupt routine to read R16/R17. Slow light pen response requires the processor software to modify the captured address read from R16/R17 by a calibration factor.

#### PROGRAMMING CONSIDERATIONS

Initialization — Registers R0-R15 must be initialized after power is turned on. The processor normally loads the CRTC registers sequentially from a firmware table. Henceforth, R0-R11 are not changed in most systems. The 6800 program in Table 3 and Figure 12 shows a typical CRTC initialization.

Hardware Scrolling — Registers R12/R13 contents determine which memory location is the first displayed character on the screen. Since the CRTC Linear Address Generator counts from this beginning count, the displayed portion of the screen may be a window on any continuous string of characters within a 16K block or refresh memory. By centering the R12/R13 pointer in the middle of the available memory space, scrolling up or down is possible . . . by line, page, or character.

#### Cursor Start Register

Example of Cursor Display Mode

Cursor End Adr. = 9

Cursor End Adr. = 10

Cursor End Adr. = 5

FIGURE 11 - INTERFACE CONTROL

#### Interlace Mode Register

| Bit<br>1 | Bit<br>0 | Mode                             |

|----------|----------|----------------------------------|

| 0<br>1   | 0        | Normal Sync Mode (Non-Interlace) |

| 0        | 1        | Interlace Sync Mode              |

| 1        | 1        | Interlace Sync & Video Mode      |

Even Odd Field Field

Normal Sync

Interlace Sync

TABLE 3 - Typical 80 x 24 Screen Format Initialization of CRTC

| Reg. # Register File  RO H Total  R1 H Displayed  R2 H Sync Position  R3 H Sync Width  R4 V Total  R5 V Total Adjust  R6 V Displayed  R7 V Sync Position  Interlace Mode  R9 Max Scan Line Address  R10 Cursor Start  R11 Cursor End  R12 Start Address (H)  R13 Start Address (L) | Program               |                 | Programm                    | ed Value      |                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|-----------------------------|---------------|-------------------------|

| Reg. #                                                                                                                                                                                                                                                                             | Register File         | Unit            | Calculation*                | Decimal       | Hex                     |

| RO                                                                                                                                                                                                                                                                                 | H Total               | T <sub>C</sub>  | 102 × 527 - 53.76 μs        | 102 - 1 = 101 | N <sub>ht</sub> = \$65  |

| R1                                                                                                                                                                                                                                                                                 | H Displayed           | τ <sub>c</sub>  | 80 x .527 = 42.16 μs        | 80            | N <sub>hd</sub> = \$50  |

| R2                                                                                                                                                                                                                                                                                 | H Sync Position       | Tc              | 86 × 527 = 45.32 μs         | 86            | N <sub>hsp</sub> = \$56 |

| R3                                                                                                                                                                                                                                                                                 | H Sync Width          | T <sub>c</sub>  | $9 \times 527 = 4.74 \mu s$ | 9             | N <sub>hsw</sub> = \$09 |

| R4                                                                                                                                                                                                                                                                                 | V Total               | Ter             | 25 x 645.12 = 16.13 ms      | 25 = 1 = 24   | N <sub>vt</sub> = \$18  |

| R5                                                                                                                                                                                                                                                                                 | V Total Adjust        | T <sub>s</sub>  | 10 x 53.76 = .54 ms         | 10            | Nadj = \$0A             |

| R6                                                                                                                                                                                                                                                                                 | V Displayed           | Ter             | 24 x 645.12 = 15.48 ms      | 24            | N <sub>vd</sub> = \$18  |

| R 7                                                                                                                                                                                                                                                                                | V Sync Position       | Tcr             | 24 x 645.12 = 15.48 ms      | 24            | N <sub>vsp</sub> = \$18 |

| R8                                                                                                                                                                                                                                                                                 | Interlace Mode        |                 |                             | _             | \$00                    |

| R9                                                                                                                                                                                                                                                                                 | Max Scan Line Address | Tsi             |                             | 11            | N <sub>s1</sub> = \$0B  |

| R10                                                                                                                                                                                                                                                                                | Cursor Start          | T <sub>sl</sub> |                             | 0             | \$00                    |

| R11                                                                                                                                                                                                                                                                                | Cursor End            | ⊤sl             |                             | 11            | \$0B                    |

| R12                                                                                                                                                                                                                                                                                | Start Address (H)     | _               |                             | 128           | \$00                    |

| R13                                                                                                                                                                                                                                                                                | Start Address (L)     |                 |                             | 128           | \$80                    |

| R14                                                                                                                                                                                                                                                                                | Cursor (H)            | -               |                             | 128           | \$00                    |

| R15                                                                                                                                                                                                                                                                                | Cursor (L)            | i i             |                             | 128           | \$80                    |

Clock Period =  $T_c$  = 527  $\mu$ s Scan Line Period =  $T_s$  =  $(N_{ht} + 1) \times T_c = 102 \times 527 \ \mu$ s = 53.76  $\mu$ s Character Row Period =  $T_{cr} = N_{sJ} \times T_{si} = 12 \times 53.76 \ \mu s = 645.12 \ \mu s$

FIGURE 12 - INITIALIZATION OF CRTC FOR 80x24 SCREEN FORMAT IN TABLE 3

| PAGE  | 001 CR  | RTINT      |       |              |                         |

|-------|---------|------------|-------|--------------|-------------------------|

| 00001 |         |            | NAM   | CRTINT       |                         |

| 00002 | 0000    |            | ORG   | <b>≱</b> ⊡   |                         |

| 00003 | 0000 SF |            | CLR B |              | CLEAR COUNTER           |

| 00004 | 0001 CE | 0020       | LDX   | #\$20        |                         |

| 00005 | 0004 F7 | 9000 CRTII | STA B | \$9000       | CRTC ADDR REG           |

| 00006 | 0007 A6 | 00         | LDA A | 0 / X        |                         |

| 00007 | 0009 B7 | 9001       | STA A | \$9001       | - ACC TO CRTC REG       |

| 00008 | 000C 08 |            | INX   |              |                         |

| 00009 |         |            | INC B |              | INC COUNTER             |

| 00010 |         | 10         | CMP B | ##10         | LAST CRTC REG?          |

| 00011 | 0010 26 | F2         | BNE   | CRTII        |                         |

|       | 0012 3F |            | 5WI   | '            |                         |

| 00013 |         |            | ORG   | <b></b> \$20 |                         |

| 00014 |         | CRTTAB     | FCB   | \$65,\$50,   | <b>≢</b> 56, <b>≢</b> 9 |

| 00015 | 0024 18 |            | FCB   | \$18,\$0A,   | \$18,\$18               |

| 00016 | 0028 00 |            | FCB   | 0,40B,0,     | <b></b> \$0B            |

| 00017 |         | 80         | FDB   | \$80,\$80    |                         |

| 00018 |         |            | END   |              |                         |

| CRTII | 0004 CF |            |       |              |                         |

TOTAL ERRORS 00000

<sup>\*</sup>These values may change according to the type of monitor.

#### **OPERATION OF THE CRTC**

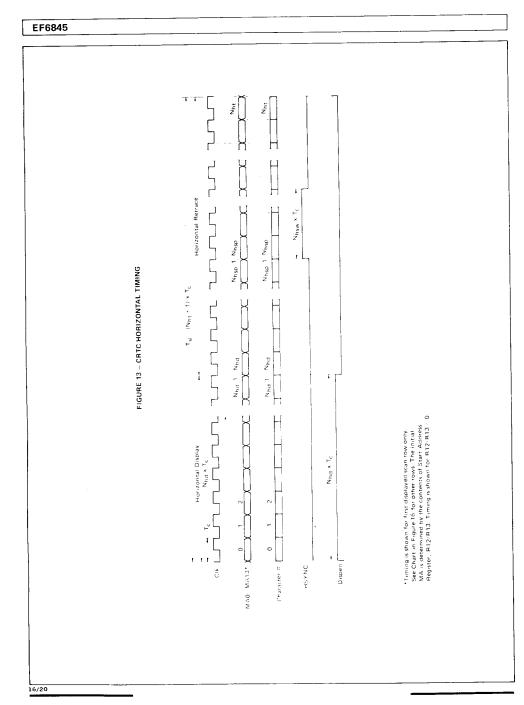

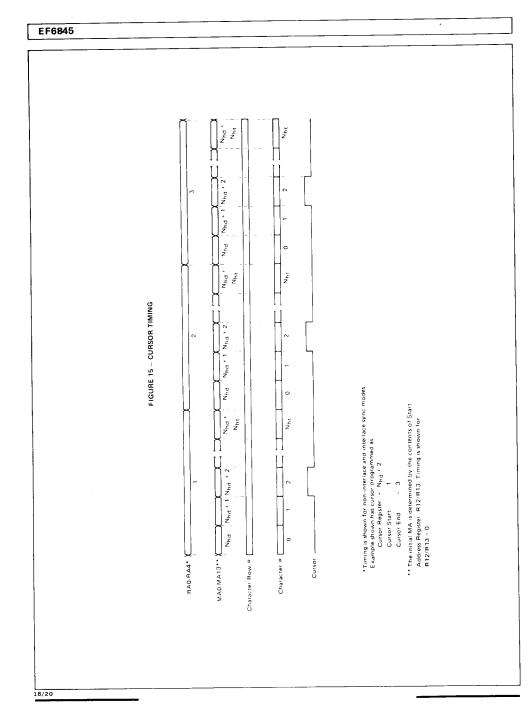

Timing Chart of the CRT Interface Signals — Timing charts of CRT interface signals are illustrated in this section with the aid of programmed example of the CRTC. When values listed in Table 4 are programmed into CRTC control registers, the device provides the outputs as

shown in the Timing Diagrams (Figures 13 through 15). The screen format of this example is shown in Figure 9. Figure 16 is an illustration of the relation between Refresh Memory Address (MAO-MA13), Raster Address (RAO-RA4) and the position on the screen. In this example, the start address is assumed to be "0".

TABLE 4 - Values Programmed Into CRTC Registers

| Rég. ≠ | Register Name         | Value               | Programmed<br>Value |

|--------|-----------------------|---------------------|---------------------|

| R0     | H. Total              | N <sub>ht</sub> +1  | Nht                 |

| R1     | H. Displayed          | Nhd                 | N <sub>hd</sub>     |

| R2     | H. Sync Position      | Nhsp                | N <sub>hsp</sub>    |

| R3     | H. Sync Width         | Nhsw                | Nhsw                |

| R4     | V. Total              | N <sub>vt</sub> + 1 | N <sub>vt</sub>     |

| R5     | V. Scan Line Adjust   | N <sub>ad)</sub>    | N <sub>adj</sub>    |

| R6     | V. Displayed          | N <sub>vd</sub>     | N <sub>vd</sub>     |

| R7     | V. Sync Position      | N <sub>vsp</sub>    | N <sub>vsp</sub>    |

| R8     | Interlace Mode        |                     |                     |

| R9     | Max Scan Line Address | N <sub>s</sub> ,    | N <sub>SI</sub>     |

| R10    | Cursor Start          |                     |                     |

| R11    | Cursor End            | 1                   |                     |

| R12    | Start Address (H)     | 0                   |                     |

| R13    | Start Address (L)     | 0                   |                     |

| R14    | Cursor (H)            |                     |                     |

| R15    | Cursor (L)            |                     |                     |

| R16    | Light Pen (H)         |                     |                     |

| R17    | Light Pen (L)         |                     |                     |

EF6845 iτ Tadi, Nadi N Tsi Freld Adjust Tome Address Continues to increment \*\*\*\* Vertical Retrace - 15 FIGURE 14 - CRTC VERTICAL TIMING TE INVITITE IN A COJ X TS 16 × 7<sub>St</sub> N VSS Freid 1 ime 2 os, ! : 15 N •••• The present CRTC freezes MA addresses at N<sub>vd</sub> × N<sub>hd</sub> "N<sub>h1</sub> must be an odd number for both interlace modes "Tintial MA is determined by R12-R13 (Start Address during vertical retrace. A design change is pending to allow MA to free run during vertical retrace time. ... Nsi must be an odd number for Interlace Sync and Register), which is zero in this timing example. Not 11 × Zha Vertical Display - Nyd x 3rr 1:0 E IS Video Mode. 0 MAD MATS .. XXC XXX L ! VSYNC (Odd Field) Video Mode Odd Field VSYNC (Even Field) -Character L Display Enable Non Interlared RAO RA4 is interlace Sync and VSYNC

| (Non Display)                    | ž   | ž                  | Pru Pru                | Nhd + Nht             | 2Nhd + Nht             | 2Nhd + Nht            |          | • | (N <sub>vd</sub> 1) × N <sub>hd</sub> + N <sub>ht</sub> | Z                  | Not x Nhd + Nht                             | N + PUN × PAN                                  | 14N + PHN × 15N                             | NX X XXX                                 | (N <sub>Vt</sub> + 1) N <sub>hd</sub> + N <sub>ht</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | #N + PUN (L + 1/N)                      |

|----------------------------------|-----|--------------------|------------------------|-----------------------|------------------------|-----------------------|----------|---|---------------------------------------------------------|--------------------|---------------------------------------------|------------------------------------------------|---------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Horizontal Retrace (Non Display) | PHZ | Nhd                | 2xN <sub>hd</sub>      | 2×N <sub>hd</sub>     | 3XN <sub>hd</sub>      | 3xN <sub>hd</sub>     |          |   | N <sub>VLL</sub> × N <sub>Pel</sub>                     | N v by N           | (N <sub>cd</sub> + 1) × N <sub>hd</sub>     | (N <sub>vd</sub> + 1) × N <sub>bd</sub>        | (N <sub>vt</sub> + 1) × N <sub>hd</sub>     | (1 · +>N)                                | (N <sub>vt</sub> + 2) × N <sub>hd</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (N <sub>V1</sub> · 2) × N <sub>h0</sub> |

|                                  |     | N <sub>bot</sub> 1 | 2×N <sub>prg</sub> - 1 | 2×N <sub>hd</sub> · 1 | 3×N <sub>hd</sub> - 1  | 3×N <sub>bd</sub> - 1 |          | - | L. P. N. N. S. V.                                       | L PHV *PAV         | (N <sub>vd</sub> + 1) × N <sub>hd</sub> + 1 | 1 - N <sub>Vd</sub> + 1) × N <sub>hq</sub> = 1 | (N <sub>ct</sub> * 1) * N <sub>hd</sub> · 1 | 1. P4N × (1 + 12N)                       | 1. N <sub>V1</sub> + 2) × N <sub>hd</sub> + 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1 Nvt + 2) × Nnd 1                      |

|                                  |     | •                  |                        |                       |                        |                       |          |   |                                                         |                    | <b>A</b>                                    |                                                |                                             |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         |

|                                  |     |                    |                        | - Fig.                | 2×N <sub>2,4</sub> · 1 | 2×N <sub>he</sub> + 1 | -        | - |                                                         | 1. Ned 1 * Ned 1.1 | Ved × Vari                                  | N <sub>vd</sub> × N <sub>hd</sub> · 1          | N N 1                                       | - × 10 × 10 × 10 × 10 × 10 × 10 × 10 × 1 | The survey of the state of the | .Not 11 x Ned 11                        |

| Character                        | 0   |                    |                        | - z                   | 2×N <sub>hd</sub>      | 2×N <sub>htt</sub>    |          | - | 2                                                       | I Not 11 - Ned     | Nvo x Nho                                   | N <sub>ed</sub> × N <sub>hd</sub>              | Not a Mind                                  | N. s. No. c.                             | F170 x 1 . 105.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 1 N N 1 1 1 N N 1 1 1 1 1 1 1 1 1 1 1 |

| mos<br>Mos<br>Juess              | 0   | z z                | 0                      | - z̄                  | 0                      | ~ <u>`</u>            | le utvaý |   | 0                                                       | - <i>3</i>         |                                             | - z                                            | a                                           | - z - z - z - z - z - z - z - z - z - z  | o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Z                                       |

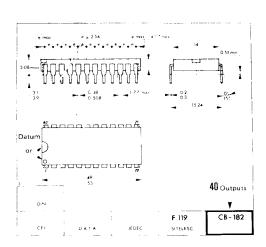

P SUFFIX

PLASTIC PACKAGE

C SUFFIX

CERAMIC PACKAGE

This is advance information and specifications are subject to change without notice. Please inquire with our sales offices about the availability of the different packages.