# MOSTEK.

# **Z80 MICROCOMPUTER PERIPHERALS**

# **Serial Timer Interrupt Controller**

**MK3801**

### EATURES

Full duplex USART with programmable DMA control signals

Two binary delay timers

Two full feature timers with

- · Delay to interrupt mode

- · Pulse width measurement mode

- Event counter mode

Eight general purpose lines with

- Full bi-directional I/O capability

- · Edge triggered interrupts on either edge

Full control of each interrupt channel

- Enable/disable

- Maskable

- Automatic end-of-interrupt mode

- Software end-of-interrupt mode

- 2.5, 4 MHz, and 6 MHz versions available

# INTRODUCTION

The MK3801 Z80 STI (Serial Timer Interrupt) is a multifunctional peripheral device for use in Z80 micro-processor based systems. It is designed to optimize current systems by reducing chip count and system costs. By providing a USART, four timers (two binary and two full function), and eight bi-directional I/O lines with individually programmable interrupts, the MK3801 can make substantial improvement to any Z80 based system.

Control and operation of the MK3801 are provided by 24 internal registers accessible by the Z80 bus. Sixteen of these registers are directly addressable and accessible; eight are indirectly addressable. Two of the four timers provide full service features, while the other two provided delay timer features only. Serial Communication is provided

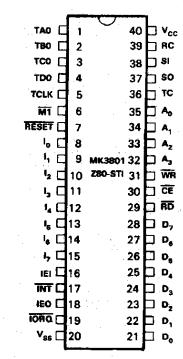

DEVICE PINOUT

by the USART, which is capable of either asynchronous or synchronous operation, optional sync word recognition and stripping, and programmable DMA control handshake lines. Eight bi-directional I/O lines provide parallel I/O capability and individually programmable interrupt capability. The interrupt structure of the device is fully programmable for all interrupts, provides for interrupt vector generation, conforms to the 280 daisy chain interrupt priority scheme, and supports automatic end of interrupt functions for the 280.

VII

| SIGNAL NAME                    | DESCRIPTION                                                                                                                                                                                                                                                                          |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>SS</sub>                | Ground                                                                                                                                                                                                                                                                               |

| V <sub>CC</sub><br>CE<br>RD    | +5 volts (± 5 percent)                                                                                                                                                                                                                                                               |

| <u>CE</u>                      | Chip Enable (Input, active low)                                                                                                                                                                                                                                                      |

| RD                             | Read Enable (Input, active low)                                                                                                                                                                                                                                                      |

| ₩R                             | Write Enable (Input, active low)                                                                                                                                                                                                                                                     |

| A <sub>0</sub> -A <sub>3</sub> | Address Inputs. Used to address one of the internal registers during a read or write<br>operation                                                                                                                                                                                    |

| D <sub>0</sub> -D <sub>7</sub> | Data Bus (bi-directional)                                                                                                                                                                                                                                                            |

| RESET                          | Device Reset (Input, active low). When activated, all internal registers (except for Times USART Data registers) will be cleared, all timers stopped, USART turned off, all interruptsdisabled and all pending interrupts cleared, and all I/O lines placed in tri-state input mode. |

| lo-l <sub>7</sub><br>INT       | General purpose I/O and interrupt lines                                                                                                                                                                                                                                              |

|                                | Interrupt Request (Output, active low, open drain)                                                                                                                                                                                                                                   |

| IORO                           | Input/Output Request from Z80-CPU (input, active low). The IORQ signal is used in conjunction with M1 to signal the MK3801 that the CPU is acknowledging its interrupt.                                                                                                              |

| IEI                            | Interrupt Enable In, active High                                                                                                                                                                                                                                                     |

| IEO                            | Interrupt Enable Out, active High                                                                                                                                                                                                                                                    |

| SO                             | Serial Output                                                                                                                                                                                                                                                                        |

| SI                             | Serial Input                                                                                                                                                                                                                                                                         |

| RC                             | Receiver Clock Input                                                                                                                                                                                                                                                                 |

| TC                             | Transmit Clock Input                                                                                                                                                                                                                                                                 |

| TAO-TDO                        | Timer Outputs                                                                                                                                                                                                                                                                        |

| TCLK                           | Timer Clock Input                                                                                                                                                                                                                                                                    |

| <b>™</b> 1                     | Z80 Machine Cycle One (Input, active low)                                                                                                                                                                                                                                            |

### **PIN DESCRIPTION**

Figure 1 illustrates the pinout of the MK3801. The functions of these individual pins are described above.

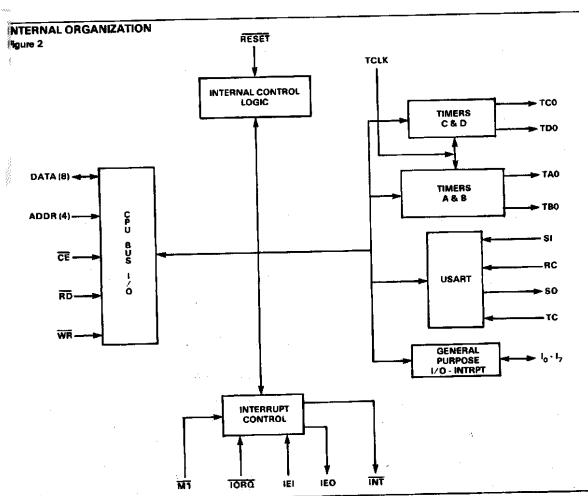

### INTERNAL ORGANIZATION

Figure 2 illustrates the MK3801 internal organization, which supports the full set of timing, communications, parallel I/O, and interrupt processing functions available in the device.

# CPU BUS I/O

The CPU BUS I/O provides the means of communications between the system and the MK3801. Data, Status, and Control Registers in the MK3801 are accessed by the bus in order to establish device parameters, assert control, and transfer status and data between the system and the MK3801.

Each register in the MK3801 is addressed over the address bus in conjunction with Chip Enable  $(\overline{CE})$ , while data is transferred over the eight bit Data bus under control of Read  $(\overline{RD})$  and Write  $(\overline{WR})$  signals.

# **REGISTER ACCESSES**

All register accesses are independent of any system clock. To read a register, both  $\overline{CE}$  and  $\overline{RD}$  must be active. The internal read control signal is essentially the combination of

both  $\overline{CE}$  and  $\overline{RD}$  active; thus the read operation will begin when the later of these two signals goes active and will end when the first signal goes inactive. The address bus must be stable prior to the start of the operation and must remain stable until the end of the operation. Unless a read operation or an interrupt acknowledge cycle is in progress, the data bus  $(D_0-D_7)$  will remain in the tri-state condition.

To write a register, both  $\overline{CE}$  and  $\overline{WR}$  must be active. The address must be stable prior to the start of the operation and must remain stable until the end of the operation. The data must be stable prior to the end of the operation and must remain stable until the end of the operation. The data presented on the bus will be latched into the register shortly after either  $\overline{WR}$  or  $\overline{CE}$  goes inactive.

# **INTERNAL REGISTERS**

There are 24 internal registers used to control the operation of the STI. Sixteen of these registers are directly addressable and accessible. Eight registers are indirectly addressable via the Pointer/Vector Register and accessible via the Indirect Data Register.

#### **DIRECTLY ADDRESSABLE REGISTERS**

The Directly Addressable Registers are accessed by placing the address of the desired register on the address lines (A<sub>0</sub>-A<sub>3</sub>) during a write or read cycle. Figure 3 lists the Directly Addressable Registers.

DIRECTLY ACCESSIBLE REGISTERS Figure 3

| ADDRESS | ABBREVIATION | REGISTER NAME                   |

|---------|--------------|---------------------------------|

| 0       | IDR          | Indirect Data Register          |

| 1       | GPIP         | General Purpose I/O-Interrupt   |

| 2       | IPRB         | Interrupt Pending Register B    |

| 3       | IPRA         | Interrupt Pending Register A    |

| 4       | ISRB         | Interrupt in-Service Register B |

| 5       | ISRA         | Interrupt in-Service Register A |

|         | IMRB         | Interrupt Mask Register B       |

| 7       | IMRA         | Interrupt Mask Register A       |

|         | PVR          | Pointer/Vector Register         |

| 9       | TABCR        | Timers A and B Control Register |

# DIRECTLY ACCESSIBLE REGISTERS (Continued)

| ABBREVIATION | REGISTER NAME               | . 25                                                                                                                                              |

|--------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| TBDR         | Timer B Data Register       |                                                                                                                                                   |

| TADR         | Timer A Data Register       | <del></del>                                                                                                                                       |

| UCR          | USART Control Register      | ·                                                                                                                                                 |

| RSR          | Receiver Status Register    | · · · · · · · · · · · · · · · · · · ·                                                                                                             |

| TSR          | Transmitter Status Register |                                                                                                                                                   |

| UDR          | USART Data Register         | بى <u>ن</u>                                                                                                                                       |

|              | TBDR TADR UCR RSR TSR       | TBDR Timer B Data Register  TADR Timer A Data Register  UCR USART Control Register  RSR Receiver Status Register  TSR Transmitter Status Register |

# INDIRECTLY ADDRESSABLE REGISTERS

| Figure - | 4 |

|----------|---|

|----------|---|

| INDIRECT ADDRESS | ABBREVIATION | REGISTER NAME                   |      |       |

|------------------|--------------|---------------------------------|------|-------|

| 0                | SCR          | Sync Character Register         |      |       |

| ĺ                | TDDR         | Timer D Data Register           |      |       |

| 2                | TCDR         | Timer C Data Register           | •    |       |

| 3                | AER          | Active Edge Register            |      |       |

| 4                | IERB         | Interrupt Enable Register B     |      |       |

| 5                | IERA         | Interrupt Enable Register A     |      |       |

| 6                | DDR          | Data Direction Register         |      |       |

| 7                | TCDCR        | Timers C and D Control Register | <br> | - 300 |

### **INDIRECTLY ADDRESSABLE REGISTERS**

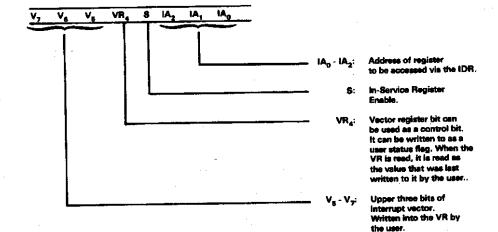

Indirectly Addressable Registers are addressed by placing the indirect address in bits IAO-IA2 of the Pointer/Vector Register, as defined in Figure 5. Data may be written to or read from the register indicated by these Indirect Register Address bits by a write or read access of the Indirect Data Register (selected when A<sub>0</sub>-A<sub>3</sub> are all zero). The indirect address bits of the Pointer/Vector Register will remain unchanged after an indirect access. Repeated accesses of the Indirect Data Register will access the same indirect register as long as the indirect address in the Pointer/Vector Register remains unchanged. The Indirectly Addressable Registers are listed in Figure 4.

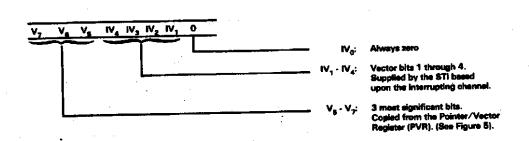

### INTERRUPT VECTOR DEFINITION

Each individual function in the MK3801 is provided with a unique interrupt vector that is presented to the system during the interrupt acknowledge cycle. The interrupt vector returned during interrupt acknowledge is formed as shown in Figure 6. There are 16 vector addresses generated internally by the MK3801, one for each of the 16 interrupt channels. The three most significant bits of these vector addresses correspond to the three most significant bits of the Pointer/Vector Register shown in Figure 5. The least significant bit of each vector address is always 0, thus producing even vector addresses. The remaining 4 bits (IV<sub>1</sub>

through IV<sub>4</sub>) identify each of the 16 interrupt channels individually. The lowest priority channel responds with 0000 for IV<sub>4</sub>-IV<sub>1</sub> respectively. The next higher priority channel responds with 0001, and so on in binary order, with the highest priority channel responding with 1111. Figure 7 lists each of the 16 interrupt channels in order of descending priority.

### INTERRUPT CONTROL REGISTERS

The Interrupt Control Registers provide control of interrupt processing for all I/O facilities of the MK3801. These registers allow the programmer to enable or disable any or all of the 16 interrupts, provide masking for any interrupts, and access to the pending or in-service status of the interrupts. Optional End-of-Interrupt modes are available under software control. The format of each of the Interrupt Control Registers is presented in Figure 8.

### INTERRUPT OPERATION

The Interrupt Enable Registers enable or disable the setting of an interrupt in the Interrupt Pending Registers. A 0 in a bit of the Interrupt Enable Registers disables the interrupt for the associated channel while a 1 enables the interrupt.

Once an interrupt is enabled, the occurrence of an interrupting condition on that channel will cause the

# POINTER/VECTOR REGISTER (PVR) Port 08 Figure 5

# INTERRUPT VECTOR

Figure 6

corresponding bit in the Interrupt Pending Register to be set. This indicates that an interrupt is pending in the MK3801.

Pending interrupts are presented to the Z80 CPU in order of priority (see Figure 1) unless they have been masked off. This is done by clearing the bit in the Interrupt Mask Register corresponding to the channel whose interrupt is to be masked. The channel's interrupt will remain pending until the mask bit for that channel is set, at which time the interrupt for that channel will be processed in order of priority.

When an interrupt vector is generated for a pending interrupt and passed to the Z80 CPU, the bit in the interrupt Pending Register, associated with the channel generating the interrupt, will be cleared. At this time, no history of the

interrupt remains in the MK3801.

In order to retain historical evidence of an interrupt being serviced by the Z8O, the In-Service Register may be enabled by setting the S-bit in the Pointer/Vector Register (see Figure 5). If the In-Service Register is enabled, the bit of the In-Service Register corresponding to the interrupting channel will be set when the interrupt vector is passed to the Z8O. At the same time, the Interrupt Pending bit will be cleared since the interrupt is now in service. The In-Service bit will be cleared on execution of a Return-from-Interrupt (H'ED4D') instruction. The In-Service Registers are directly addressable, and the In-Service bit for any interrupt may be cleared by writing to the In-Service Register if the Return-from-Interrupt instruction is not used.

# INTERRUPT CONTROL REGISTER DEFINITIONS

Figure 7

There are sixteen interrupt channels on the STI arranged in the following priority:

| PRIORITY | CHANNEL | DESCRIPTION                                   | ALTERNATE USAGE |

|----------|---------|-----------------------------------------------|-----------------|

| HIGHEST  | 1111    | General Purpose Interrupt 7 (I <sub>2</sub> ) |                 |

|          | 1110    | General Purpose Interrupt 6 (Is)              |                 |

|          | 1101    | Timer A                                       |                 |

|          | 1100    | Receive Buffer Full                           |                 |

|          | , 1011  | Receive Error                                 |                 |

|          | 1010    | Transmit Buffer Empty                         |                 |

|          | 1001    | Transmit Error                                |                 |

|          | 1000    | Timer B                                       |                 |

|          | 0111    | General Purpose Interrupt 5 (ls)              |                 |

|          | 0110    | General Purpose Interrupt 4 (I <sub>4</sub> ) | TA (PW-Event)   |

|          | 0101    | Timer C                                       | •               |

|          | 0100    | Timer D                                       |                 |

|          | 0011    | General Purpose Interrupt 3 (I <sub>3</sub> ) | TB (PW-Event)   |

|          | 0010    | General Purpose Interrupt 2 (l <sub>2</sub> ) |                 |

| * .      | 0001    | General Purpose Interrupt 1 (I <sub>1</sub> ) | DMA (TR)TX      |

| LOWEST   | 0000    | General Purpose Interrupt 0 (I <sub>0</sub> ) | DMA (RR)REC     |

# INTERRUPT CONTROL REGISTERS Figure 8

| Α | DDR | ESS. |

|---|-----|------|

|   |     |      |

|   |     |      |

| DDRESS             |                      |           |            | INT   | ERRUPT EN                    | ABLE REGIST               | ERS .                   | <b>.</b>      | -            |

|--------------------|----------------------|-----------|------------|-------|------------------------------|---------------------------|-------------------------|---------------|--------------|

|                    |                      | 7         | 6          | 5     | 4                            | 3                         | 2                       | - 1           | 0            |

| Indirect<br>Port 5 | A<br>(IERA)          | GPIP<br>7 | GPIP<br>6  | TIMER | RCV<br>Buffer<br>Full        | RCV<br>Error              | XMIT<br>Buffer<br>Empty | XMIT<br>Error | TIMER<br>B   |

| Indirect<br>Port 4 | 8<br>(IER <b>9</b> ) | GPIP<br>6 | GPIP<br>4  | TIMER | TIMER.<br>D                  | GPIP<br>3                 | GPIP<br>2               | GPIP<br>1     | GPIP<br>0    |

|                    | ·                    |           | •          | IN T  | ERRUPT M                     | ASK REGIST                | ERS                     | <del>'</del>  |              |

|                    |                      | 7         | 6          | 5     | 4                            | 3                         | 2                       | 1             | 0            |

| Port 7             | A<br>(IMRA)          | GMP<br>7  | GPIP<br>6  | TIMER | RCV<br>Buffer<br>Full        | RCV<br>Error              | XMIT<br>Buffer<br>Empty | XMIT<br>Error | TIMER        |

| Port 6             | B<br>(IMRB)          | GPIP<br>5 | GPIP<br>4  | TIMER | TIMER<br>D,                  | GPIP<br>3                 | GPIP<br>2               | GPIP          | GPIP<br>0    |

|                    |                      |           |            |       |                              | D, C = MASI<br>DING REGIS |                         |               | <del>'</del> |

| and the state of   |                      | _ 7       | 5 <b>6</b> | Б     | 4                            | 3                         | * <b>2</b>              | 1.            | . 0          |

| Port 3             | (IPRA)               | GPIP<br>7 | GPIP<br>6  | TIMER | RCV<br>Buffer<br>Full        | RCV<br>Error              | XMIT<br>Buffer<br>Empty | XMIT<br>Error | TIMER<br>B   |

| Port 2             | B<br>(IPRB)          | GPIP<br>5 | GPIP<br>4  | TIMER | TIMER<br>D                   | GPIP<br>3                 | GPIP<br>2               | GPIP<br>1     | GPIP<br>0    |

|                    | ;                    | *         |            |       | RITING 0 = C<br>RITING 1 = U | LEAR<br>INCHANGED         | <del>'</del>            |               |              |

Figure 10

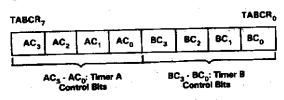

# TIMER A and B CONTROL REGISTER (TABCR) Port 9 Figure 9

The four control bits are used to select the timer mode and prescale value, as follows:

# **CONTROL BIT DEFINITION**

| C <sup>3</sup> | C, | C1 | Co        |                                 |

|----------------|----|----|-----------|---------------------------------|

|                |    |    |           | Times Stenned                   |

| 0              | 0  | 0  | 0         | Timer Stopped                   |

| 0              | 0  | 0  | 1         | Delay Mode, ÷4 Prescale         |

| 0              | 0  | 1  | 0         | Delay Mode, ÷10 Prescale        |

| 0              | 0  | 1  | 1         | Delay Mode, ÷16 Prescale        |

| 0              | 1  | 0  | 0         | Delay Mode, ÷50 Prescale        |

| ō              | 1  | 0  | 1         | Delay Mode, ÷64 Prescale        |

| ō              | 1  | 1  | 0         | Delay Mode, ÷100 Prescale       |

| ō              | 1  | 1  | 1         | Delay Mode, ÷200 Prescale       |

| 1              | Ó  | 0  | 0         | Event Count Mode                |

| 1              | 0  | 0  | . 1       | Pulse Width Mode, ÷4 Prescale   |

| 1              | 0  | 1  | 0         | Pulse Width Mode, ÷10 Prescale  |

| 1              | Ō  | 1  | <b>`1</b> | Pulse Width Mode, +16 Prescale  |

| 1              | 1  | 0  | 0         | Pulse Width Mode, ÷50 Prescale  |

| 1              | 1  | Ó  | 1         | Pulse Width Mode, +64 Prescale  |

| 1              | 1  | 1  | 0         | Pulse Width Mode, ÷100 Prescale |

|                | 4  | 4  | 1         | Pulse Width Mode ÷200 Prescale  |

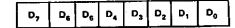

# TIMER A DATA REGISTER AND TIMER B DATA REGISTER (TADR, TBDR) Port 8 & Port A

| 1 | D, | D <sub>6</sub> | D <sub>6</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | ٦, | Do |  |

|---|----|----------------|----------------|----------------|----------------|----------------|----|----|--|

# TIMERS

Four timers are available on the MK3801. Two provide full service features including delay timer operation, event counter operation, pulse width measurement operation, and pulse generation. The two other timers provide delay timer features only, and may be used for baud rate generators for use with the USART.

All timers are prescaler/counter timers, with a common independent clock input, and are not required to be operated

# TIMER C and D CONTROL REGISTER (TCDCR) Indirect Port 7

| TCDCR,   |                     |                      |       |                  |                 | TC                   | DCR   |

|----------|---------------------|----------------------|-------|------------------|-----------------|----------------------|-------|

| TIMER A  | CC2                 | cc,                  | cc    | TIMER B<br>RESET | DC <sub>2</sub> | DC <sub>1</sub>      | DCo   |

| <u> </u> | CC <sub>2</sub> · C | C <sub>o</sub> : Tir | mer C |                  | DC <sub>2</sub> | DC <sub>0</sub> : Ti | mer D |

Three control bits are used to control each timer, as defined below:

### CONTROL BIT DEFINITION

| $C_2$ | C <sub>1</sub> | Co |                           |

|-------|----------------|----|---------------------------|

| ō     | o              | o  | Timer Stopped             |

| 0     | 0              | 1  | Delay Mode, ÷4 Prescale   |

| 0     | 1              | 0  | Delay Mode, ÷10 Prescale  |

| 0     | 1              | 1  | Delay Mode, +16 Prescale  |

| 1     | 0              | 0  | Delay Mode, ÷50 Prescale  |

| 1     | 0              | 1  | Delay Mode, ÷64 Prescale  |

| 1     | 1              | 0  | Delay Mode, ÷100 Prescale |

| 1     | 1              | 1  | Delay Mode, ÷200 Prescale |

TIMER C DATA REGISTER and TIMER D DATA REGISTER (TCDR, TDDR) Indirect, Port 2 and Indirect Port 1

from the system clock. In addition, all timers have a time-out output function that toggles each time the timer times out.

# TIMER CONTROL REGISTERS

The 4 timers (A,B,C, and D) are programmed via 2 control registers and 4 timer data registers. Timers A and B are controlled by a single register (TABCR) and two timer data registers (TADR,TBDR). Timers C and D are controlled by a second control register (TCDCR) and two timer data

registers (TCDR, TDDR). Bits in the control registers allow the selection of operational mode, prescale, and control, while the data registers are used to read the timer or write the time constant register. General Purpose I/O Interrupt pins 3 (TB) and 4 (TA) are used for timer B and A inputs in event and pulse width modes. Figure 9 illustrates the Control and Data Register for timers A and B, while Figure 10 illustrates the Control and Data registers for timers C and D.

#### **USART**

Serial Communication is provided by the USART, which is capable of either asynchronous or synchronous operation. Variable word width and start/stop bit configurations are available under software control for asynchronous operation. For synchronous operation, a Sync Word is provided to establish synchronization during receive operations. The Sync Word will also be repeatedly transmitted when no other data is available for transmission. Operational modes exist to allow stripping of all Sync Words received in synchronous operation, and to allow the operation of DMA control handshake lines by the USART through General Purpose I/O Port lines 0 and 1. Separate receive and transmit clocks are available, and

separate receive and transmit status and data bytes allow independent operation of the transmit and receive sections.

### **USART CONTROL REGISTERS**

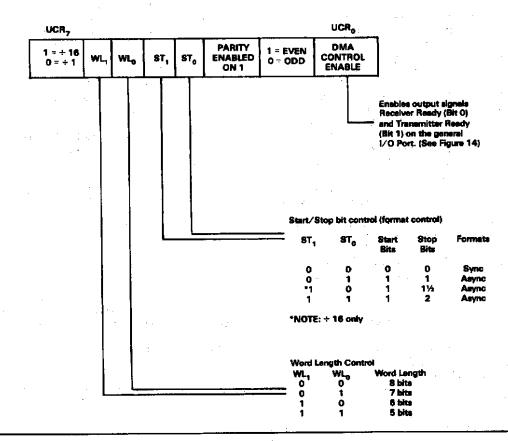

The USART is provided with 3 control/status registers and a data register. The programmer may specify operational parameters for the USART via the Control Register, as shown in Figure 11. Status of both the Receiver and Transmitter sections is accessed by means of the 2 Status Registers, as shown in Figure 12. Data written to the Data Register is passed to the transmitter, while reading the data register will access data received by the USART. The USART Data Register form is illustrated in Figure 13.

#### **ERROR CONDITIONS**

Error conditions in the USART are determined by monitoring the Receive Status Register (Port D) and the Transmitter Status Register (Port E). These error conditions are only valid for each word boundary and are not latched When executing block transfers of data, it is necessary to save any errors so that they can be checked at the end of block. In order to save error conditions during data transfer the STI interrupt controller may be used by enabling error.

USART CONTROL REGISTER (UCR) Port C Figure 11

#### RECEIVER STATUS REGISTER (RSR) Port D Figure 12 RSR RSR, RECEIVER MATCH/CHARACTER SYNC STRIP FOUND/SEARCH OVERRUN PARITY FRAME BUFFER ENABLE ENABLE IN PROGRESS OR BREAK DETECT ERROR ERROR ERROR **FULL** TRANSMITTER STATUS REGISTER (TSR) Port E TSA TSR. TRANSMITTER UNDERRUN AUTO END OF HIGH LOW RUFFER BREAK ENABLE TRANSMISSION ERROR TURNAROUND EMPTY Serial Output State 0 Low ("0") 0 \*Connects transmitter output to receiver input. In loopback mode, transmitter goes high when disabled. Also connects clocks with TC given priority. USART DATA REGISTER (UDR) Port F Figure 13

# GENERAL PURPOSE I/O CONTROL REGISTERS

D,

D<sub>0</sub>

Figure 14

1 = RISİNG 0 = FALLING

1 = OUTPUT 0 = INPUT

| •         | AC        | TIVE EDGE C | ONTROL RE   | GISTER (AE | R) Indirect Po | n 3       |           |

|-----------|-----------|-------------|-------------|------------|----------------|-----------|-----------|

| GPIP<br>7 | GPIP<br>6 | GPIP<br>5   | GPIP<br>4   | GPIP<br>3  | GPIP<br>2      | GPIP<br>1 | GPIP<br>0 |

|           |           | DATA DIREC  | TION REGIS  | TER (DDR)  | ndirect Port 6 |           |           |

| GPIP<br>7 | GPIP<br>6 | GPIP<br>5   | GPIP<br>4   | GPIP<br>3  | GPIP<br>2      | GPIP<br>1 | GPIP<br>0 |

|           | GE        | NERAL PUR   | POSE I/O DA | ATA REGIST | ER (GPIP) Po   | rt 1      |           |

| GPIP      | GPUP      | GPIP        | GPIP        | GPIP       | GPIP           | GPIP      | GPIP      |

D,

D<sub>3</sub>

3

TIMER B

INPUT

D,

interrupts (Port 5, Indirect) for the desired channel (Receive error or Transmit error) and by masking these bits off (Port 7). Once the transfer is complete, the Interrupt Pending Register (Port 3) can be polled to determine the presence of

$\mathbf{D}_{\mathbf{5}}$

Б

# a pending error interrupt, and therefore an error. GENERAL PURPOSE I/O - INTERRUPT PORT

The General Purpose I/O - Interrupt Port provides eight I/O lines that may be operated either as inputs or outputs under software control. In addition, each line may generate an interrupt on either a positive going edge or a negative going edge of the input signal.

Two of the lines in this port provide auxiliary input functions for the timers in the pulse width measurement mode and the event counter mode. Two others serve as auxiliary output lines for the USART, one indicating the Receive

Buffer Full condition (RR) and the other indicating the Transmitter Buffer Empty condition (TR). These may be used as handshake signals for a DMA controller or other external control circuitry.

D<sub>D</sub>

(RR

D.

# GENERAL PURPOSE I/O CONTROL REGISTERS

The General Purpose I/O and Interrupt Port has 2 control registers. One allows the programmer to specify the Active Edge for each bit that will trigger the interrupt associated with that bit. The other register specifies the Data Direction (input and output) associated with each bit. The third register is the actual data I/O register used to input or output data to the port. When the USART is programmed to use DMA signals, this overrides the GPIP data and the DDR. The General Purpose I/O Control and Data Registers are illustrated in Figure 14.

### **MK3801 ELECTRICAL SPECIFICATIONS**

# ABSOLUTE MAXIMUM RATINGS -25°C to + 100° Temperature Under Bias -25°C to + 100° Storage Temperature -65°C to + 150° Voltage on Any Pin with Respect to Ground -3 V to + 7

### D.C. CHARACTERISTICS

$T_A$  = 0°C to 70°C,  $V_{CC}$  = +5 V  $\pm$  5% unless otherwise specified.

| SYM              | PARAMETER                                 | MIN  | MAX                  | UNIT | TEST<br>CONDITION                        |

|------------------|-------------------------------------------|------|----------------------|------|------------------------------------------|

| V <sub>IH</sub>  | Input High Voltage                        | 2.0  | V <sub>CC</sub> + .3 | V    | •                                        |

| V <sub>IL</sub>  | Input Low Voltage                         | -0.3 | 0.8                  | V    |                                          |

| V <sub>OH</sub>  | Output High Voltage                       | 2.4  |                      | V    | I <sub>OH</sub> = -120 μA                |

| V <sub>OL</sub>  | Output Low voltage                        |      | 0.4                  | V    | I <sub>OL</sub> = 2.0 mA                 |

| I <sub>LL</sub>  | Power Supply Current                      |      | 180                  | mA   | Outputs Open                             |

| lu               | Input Leakage Current                     |      | ±10                  | ДΑ   | V <sub>IN</sub> = 0 to V <sub>CC</sub>   |

| I <sub>LOH</sub> | Tri-State Output Leakage Current in Float |      | 10                   | μÁ   | V <sub>OUT</sub> =2.4 to V <sub>OC</sub> |

| ILOL             | Tri-State Output Leakage Current in Float |      | -10                  | μА   | V <sub>OUT</sub> = 0.4 V                 |

All voltages are referenced to ground.

### CAPACITANCE

$T_A = 25$ °C, f = 1 MHz unmeasured pins returned to ground.

| SYM  | PARAMETER             |          | e de la companya de l | MAX    | UNIT | TEST<br>CONDITION     |

|------|-----------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|-----------------------|

| CIN  | Input Capacitance     |          | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10     | pf   | Unmeasured<br>pins    |

| Соит | Tri-state Output Capa | scitance |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <br>10 | pf   | returned to<br>ground |

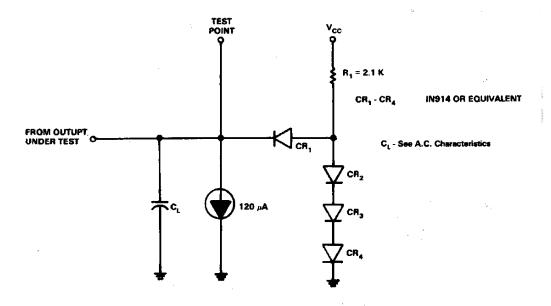

A.C. CHARACTERISTICS  $T_A = 0^{\circ}\text{C to } 70^{\circ}\text{C, V}_{\text{CC}} = +5 \text{ V} \pm 5\% \text{ unless otherwise noted.}$

|                                |                                           |                                                                        | MK3801-0 MK |     | MK38 | MK3801-4 MK3801-6 |     |          | ÷ "  | l                   |  |

|--------------------------------|-------------------------------------------|------------------------------------------------------------------------|-------------|-----|------|-------------------|-----|----------|------|---------------------|--|

| SIGNAL                         | SYMBOL                                    | PARAMETER                                                              | MIN         | MAX | MIN  | MAX               | MIN | MAX      | UNIT | CONDITION           |  |

| ∆ <sub>0</sub> -A <sub>3</sub> | T <sub>SAR</sub><br>&<br>T <sub>SAW</sub> | Address setup time prior to falling edge of CEWR or CERD               | 80          |     | 30   |                   | 15  |          | ns   |                     |  |

|                                | T <sub>HAR</sub><br>&<br>T <sub>HAW</sub> | Address hold time<br>after rising edge of<br>CEWR or CERD              | 0           |     | 0    |                   | 0   |          | ns   |                     |  |

| CEWR                           | T <sub>WL</sub>                           | CEWR pulse width low (write cycle)                                     | 360         |     | 205  |                   | 175 |          | กร   | Note 1              |  |

|                                | Tww                                       | CEWR high time<br>between write cycles                                 | 580         |     | 400  |                   | 300 |          | ns   | Note 1              |  |

|                                | T <sub>WRD</sub>                          | CEWR high to CERD low                                                  | 580         |     | 400  |                   | 300 |          | ns   |                     |  |

| CERD                           | T <sub>RDL</sub>                          | CERD pulse width low (read cycle)                                      | 400         |     | 250  |                   | 215 |          | ns   | Note 1              |  |

|                                | TRR                                       | CERD high time<br>between read cycles                                  | 300         |     | 200  |                   | 190 |          | ns   |                     |  |

|                                | T <sub>M1RD</sub>                         | Rising M1RD to falling M1RD                                            | 225         |     | 165  |                   | 95  |          | ns   | ;                   |  |

|                                | T <sub>RDW</sub>                          | CERD high to CEWR                                                      | 125         |     | 100  |                   | 75  |          |      |                     |  |

| M1                             | T <sub>SM1</sub>                          | M1 setup time prior to<br>falling IORQ during<br>interrupt acknowledge | 800         |     | 500  |                   | 350 |          | ns   | ·.                  |  |

| IORQ                           | TIOL                                      | IORQ low time                                                          | 300         |     | 185  |                   | 170 | [44      | ns   |                     |  |

| IEI                            | T <sub>SIEI</sub>                         | Setup to falling IORO during interrupt acknowledge                     | 140         |     | 80   |                   | 65  |          | ns   |                     |  |

|                                | TSRD                                      | Setup prior to end of<br>4D read on RETI                               | 100         |     | 50   |                   | 40  | <u> </u> | ns   |                     |  |

| D <sub>0</sub> -D <sub>7</sub> | T <sub>SDM1</sub>                         | Data valid prior to<br>rising RD (M1 cycle)                            | 65          |     | 50   |                   | 45  |          | ns   | Load<br>100 pf<br>+ |  |

|                                | T <sub>HDM1</sub>                         | Data hold time after rising RD (M1 cycle)                              | 0           |     | 0    |                   | 0   |          | ns   | 1 TTL load          |  |

|                                | TDRD                                      | Data output delay from CERD                                            |             | 400 | 1    | 250               |     | 215      | ns   |                     |  |

|                                | T <sub>SDW</sub>                          | Data setup time to rising edge of CEWR                                 | 350         |     | 280  |                   | 175 |          | ns   |                     |  |

|                                | T <sub>HDW</sub>                          | Data hold time from rising edge of CEWR                                | 0           |     | 0    |                   | 0   |          | ns   |                     |  |

|                                | T <sub>DDI</sub>                          | Data output delay from<br>falling IORQ during<br>interrupt acknowledge | 1           | 300 |      | 185               |     | 170      | ns   |                     |  |

# A.C. CHARACTERISTICS (Continued)

|                   |                     |                                                                                   | MK3801-0 |                            | MK3801-4 |                            | MK3801-6 |                            |      |                                                  |  |

|-------------------|---------------------|-----------------------------------------------------------------------------------|----------|----------------------------|----------|----------------------------|----------|----------------------------|------|--------------------------------------------------|--|

| SIGNAL            | SYMBOL              | PARAMETER                                                                         | MIN      | MAX                        | MIN      | MAX                        | MIN      | MAX                        | UNIT | CONDITION                                        |  |

|                   | T <sub>DHIV</sub> Z | Data hold time following M1 IORQ during interrupt acknowledge cycle.              | 0        |                            | 0        |                            | 0        |                            | ns   |                                                  |  |

|                   | T <sub>DOZ</sub>    | Delay to float                                                                    |          | 150                        |          | 100                        |          | - 80                       | ns   |                                                  |  |

| lo-l <sub>7</sub> | T <sub>IPW</sub>    | Minimum active pulse width                                                        | 200      |                            | 100      |                            | 90       |                            | ns   |                                                  |  |

|                   | TICY                | Minimum time between active edges                                                 | 200      |                            | 100      |                            | 90       |                            | ns   | -                                                |  |

|                   | Tow                 | Data valid from rising CEWR                                                       |          | 600                        |          | 500                        |          | 400                        | ns   | Load<br>100 pf<br>+ 1 TTL                        |  |

| RR                | TDRR                | Delay from rising RC                                                              |          | 360                        |          | 240                        |          | 195                        | ns   | 1 TTL                                            |  |

| TR                | T <sub>DTR</sub>    | Delay from rising TC                                                              |          | 450                        |          | 295                        |          | 240                        | ns   |                                                  |  |

| TA0-TD0           |                     | Timer output low from rising edge of CEWR (A & B) (Reset TOUT)                    |          | 600                        |          | 500                        |          | 400                        | ns   | Load<br>100 pf<br>+                              |  |

|                   | τ <sub>οπ</sub>     | Tout valid from<br>Internal timeout                                               |          | 2 t <sub>CLK</sub><br>+400 |          | 2 t <sub>CLK</sub><br>+300 |          | 2 t <sub>CLK</sub><br>+250 | ns   | 1 TTL load                                       |  |

| TÇLK              | T <sub>CLKL</sub>   | Low time                                                                          | 130      |                            | 95       |                            | 76       |                            | ns   |                                                  |  |

|                   | T, CLKH             | High time                                                                         | 130      |                            | 95       |                            | 75       |                            | ns   |                                                  |  |

|                   | T <sub>tCKC</sub>   | Cycle time                                                                        | 300      | 2500                       | 200      | 2500                       | 165      | 2500                       | ns   |                                                  |  |

| RESET             | T <sub>RSL</sub>    | Low time for part reset                                                           | 3        |                            | 2        |                            | 1.6      | <u></u>                    | \$aq |                                                  |  |

| IEO               | TDIEOH              | IEO delay from rising edge of IEI                                                 |          | 200                        |          | 130                        |          | 100                        | ns   | Load<br>100 pf<br>+                              |  |

| :                 | T <sub>DIEOL</sub>  | IEO delay from falling<br>edge of IEI                                             |          | 200                        |          | 130                        |          | 100                        | ns   | 1 TTL load                                       |  |

|                   | T <sub>DIEOM</sub>  | IEO delay from falling<br>edge of M1 (interrupt<br>occurring just prior to<br>M1) |          | 270                        | ;        | 190                        |          | 110                        | ns   |                                                  |  |

|                   | <sup>T</sup> DIEOA  | Delay to rising IEO from rising IORQ during interrupt acknowledge                 |          | 1000                       |          | 800                        |          | 600                        | ns   |                                                  |  |

|                   | T <sub>DIEOR</sub>  | Delay to rising IEO<br>from rising edge of RD<br>during ED fetch of<br>RETI       |          | 500                        |          | 400                        |          | 300                        | ns   |                                                  |  |

| ĪNŦ               | TDOX                | Delay to falling INT from external inter-<br>rupt active transition               |          | 550                        |          | 380                        |          | 300                        | ns   | Open drain<br>load 100 pf<br>+<br>2.1 K resistor |  |

# .C. CHARACTERISTICS (Continued)

| SIGNAL |                  |                                                                                             | MK3801-0 |     | MK3801-4 |        | MK3801-6 |     |      |                        |  |

|--------|------------------|---------------------------------------------------------------------------------------------|----------|-----|----------|--------|----------|-----|------|------------------------|--|

|        | SYMBOL           | PARAMETER                                                                                   | MIN      | MAX | MIN      | MAX    | MIN      | MAX | UNIT | CONDITION              |  |

|        | T <sub>Dii</sub> | Delay to falling INT<br>from internal inter-<br>rupt transition                             |          | 360 |          | 280    |          | 250 | ns   |                        |  |

|        | T <sub>DTI</sub> | Transmitter Internal interrupt transition delay from rising or falling edge of TC           |          | 560 |          | 390    |          | 360 | ns   |                        |  |

|        | T <sub>DRI</sub> | Receiver buffer full<br>internal interrupt<br>transition delay<br>from rising edge<br>of RC |          | 400 | :        | 300    |          | 270 | пş   |                        |  |

|        | TDREI            | Receiver error<br>internal interrupt<br>transition delay<br>from falling edge<br>of RC      |          | 550 |          | 430    |          | 400 | ns   |                        |  |

| SI     | T <sub>SSI</sub> | Serial in set up time<br>to rising edge of RC<br>(Divide by one only)                       | 80       |     | 80       |        | 55       |     | ns   |                        |  |

|        | T <sub>HSI</sub> | Data hold time from<br>rising edge of RC<br>(Divide by one only)                            | 400      |     | 350      | ļ.<br> | 300      |     | ns   | 6                      |  |

| so     | Toso             | Data valid from falling edge of TC                                                          |          | 420 |          | 390    |          | 345 | ns   | 100 pf + 1 TTL<br>load |  |

| TC     | TTCL             | Low time                                                                                    | 650      |     | 500      |        | 400      |     | ns   |                        |  |

|        | ттсн             | High time                                                                                   | 650      | ľ   | 500      |        | 400      |     | ns   |                        |  |

|        | TTCCY            | Cycle time                                                                                  | 1.5      |     | 1.05     |        | .85      |     | μs   |                        |  |

| RC     | T <sub>RCL</sub> | Low time                                                                                    | 650      |     | 500      |        | 400      | -   | ns   |                        |  |

|        | T <sub>RCH</sub> | High time                                                                                   | 650      |     | 500      |        | 400      |     | ns   |                        |  |

|        | TRCCY            | Cycle time                                                                                  | 1.5      | 1   | 1.05     |        | .85      |     | μS   |                        |  |

NOTE: All A.C. measurements are referenced to  $V_{IL}$  max.,  $V_{HH}$  min.,  $V_{QL}$  (0.8 V), or  $V_{QH}$  (2.0 V).

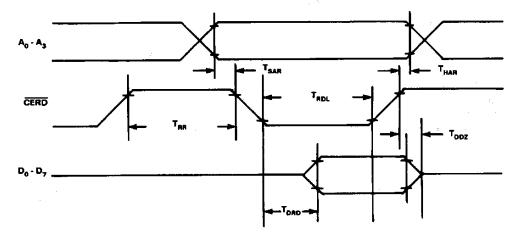

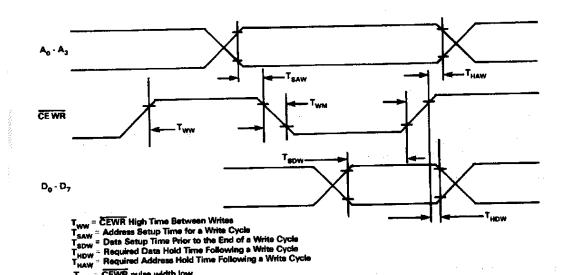

| TIMING DIAGRAMS                                                                     |                |              |                |

|-------------------------------------------------------------------------------------|----------------|--------------|----------------|

| Figure 16                                                                           |                | <b>"1"</b> . | "0"            |

| Timing measurements are made at the following voltages, unless otherwise specified: | OUTPUT         | 2.0 V        | 0.8 V          |

| READ CYCLE                                                                          | INPUT<br>FLOAT | 2.0 V        | 0.8 V<br>0.5 V |

|                                                                                     |                |              |                |

T<sub>SAR</sub> = Address Setup Time for a <u>Reed</u> Cycle

T<sub>DRD</sub> = Data Output Delay from CERD

T<sub>DDZ</sub> = Time to Tri-State Following a Read Cycle

T<sub>HAR</sub> = Required Address Hold Time Following a Read Cycle

T<sub>WM</sub> = CEWR pulse width low

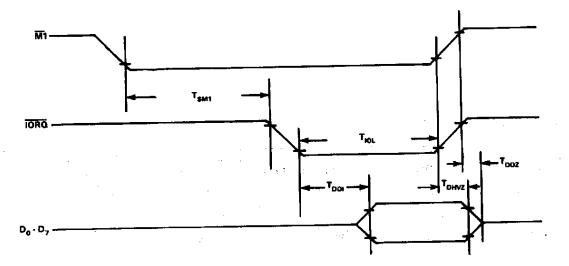

# **INTERRUPT ACKNOWLEDGE CYCLE** Figure 18

T<sub>IOL</sub> = IORQ Pulse Width Low

T<sub>SM</sub> = M1 Setup Time prior to IORQ For an Acknowledge cycle

T<sub>DDI</sub> = Access Time for Vector

T<sub>DD2</sub> - Time to Tri-State Following a Vector

T<sub>DHV2</sub> = Data hold time following M1 IORQ during interrupt acknowledge cycle

### **TIMER A.C. CHARACTERISTICS**

### Definitions:

Error = Indicated Time Value - Actual Time Value

tpsc = t<sub>CUK</sub> x Prescale Value

### Internal Timer Mode

| er en       |                                                                     |

|-------------------------------------------------|---------------------------------------------------------------------|

| Single Interval Error (free running) (Note 2)   | ± 100 ns                                                            |

| Cumulative Internal Error                       |                                                                     |

| Error Between Two Timer Reads                   | $\pm (tpsc + 4 t_{CLK})$                                            |

| Start Timer to Stop Timer Error                 | 2 t <sub>CLK</sub> + 100 ns to -(tpsc + 6t <sub>CLK</sub> + 100 ns) |

| Start Timer to Read Timer Error                 | 0 to -(tpsc + 6 t <sub>CLK</sub> + 400 ns)                          |

| Start Timer to Interrupt Request Error (Note 3) | 2 t <sub>CLK</sub> to -(4t <sub>CLK</sub> +800 ns)                  |

| Pulse Width Measurement Mode                    |                                                                     |

| Measurement Accuracy (Note 1)                   | 2 t <sub>CLK</sub> to -{tpsc + 4t <sub>CLK</sub> }                  |

| Winimum Pulse Yvidin                            | CLK                                                                 |

| Event Counter Mode                              |                                                                     |

- NOTES:

1. Error may be cumulative if repetitively performed.

2. Error with respect to T<sub>OUT</sub> or INT if note 3 is true.

3. Assuming it is possible for the timer to make an interrupt request immediately.

# ORDERING INFORMATION

| PART NO.           | DESIGNATOR     | PACKAGE TYPE    | MAX CLOCK<br>FREQUENCY | TEMPERATURE<br>RANGE |  |

|--------------------|----------------|-----------------|------------------------|----------------------|--|

| MK3801 N-0 Z80-STI |                | Plastic 2.5 MHz |                        | 0 to 70°C            |  |

| MK3801N-4          | <b>Ζ8</b> 0-SΠ | Plastic 4.0 MHz |                        | 0 to 70°C            |  |

| MK3801N-6          | Z80-STI        | Plastic         | 6.0 MHz                | 0 to 70°C            |  |